Intel 8086-1 Bedienungsanleitung

Stöbern Sie online oder laden Sie Bedienungsanleitung nach Hardware Intel 8086-1 herunter. Intel 8086-1 User Manual [en] Benutzerhandbuch

- Seite / 30

- Inhaltsverzeichnis

- LESEZEICHEN

- 16-BIT HMOS MICROPROCESSOR 1

- 8086/8086-2/8086-1 1

- ). Only the pin 5

- FUNCTIONAL DESCRIPTION 6

- General Operation 6

- MINIMUM AND MAXIMUM MODES 7

- 231455–5 8

- 231455–6 8

- 231455–8 9

- External Interface 10

- 231455–9 11

- Basic System Timing 12

- ABSOLUTE MAXIMUM RATINGS* 14

- D.C. CHARACTERISTICS (8086: T 14

- A.C. CHARACTERISTICS (8086: T 15

- TIMING RESPONSES 16

- (Continued) 16

- WAVEFORMS 17

- WAVEFORMS (Continued) 18

- A.C. CHARACTERISTICS 19

- Mnemonics 26

- Intel, 1978 26

- offset-high 28

- DATA SHEET REVISION REVIEW 30

Inhaltsverzeichnis

September 1990 Order Number: 231455-005808616-BIT HMOS MICROPROCESSOR8086/8086-2/8086-1YDirect Addressing Capability 1 MByteof MemoryYArchitecture Des

8086Status bits S3through S7are multiplexed with high-order address bits and the BHEsignal, and aretherefore valid during T2through T4.S3and S4indi-ca

8086MASKABLE INTERRUPT (INTR)The 8086 provides a single interrupt request input(INTR) which can be masked internally by softwarewith the resetting of

8086EXTERNAL SYNCHRONIZATION VIA TESTAs an alternative to the interrupts and general I/Ocapabilities, the 8086 provides a single software-testable inp

8086lines D7–D0as supplied by the inerrupt system logic(i.e., 8259A Priority Interrupt Controller). This byteidentifies the source (type) of the inter

8086ABSOLUTE MAXIMUM RATINGS*Ambient Temperature Under Bias ÀÀÀÀÀÀ0§Cto70§CStorage Temperature ÀÀÀÀÀÀÀÀÀÀb65§Ctoa150§CVoltage on Any Pin withRespect t

8086A.C. CHARACTERISTICS (8086: TAe0§Cto70§C, VCCe5Vg10%)(8086-1: TAe0§Cto70§C, VCCe5Vg5%)(8086-2: TAe0§Cto70§C, VCCe5Vg5%)MINIMUM COMPLEXITY SYSTEM T

8086A.C. CHARACTERISTICS (Continued)TIMING RESPONSESSymbol Parameter8086 8086-1 8086-2UnitsTestMin Max Min Max Min MaxConditionsTCLAV Address Valid De

8086A.C. TESTING INPUT, OUTPUT WAVEFORM231455-11A.C. Testing: Inputs are driven at 2.4V for a Logic ‘‘1’’ and 0.45Vfor a Logic ‘‘0’’. Timing measureme

8086WAVEFORMS (Continued)MINIMUM MODE (Continued)231455–14SOFTWARE HALTÐRD, WR, INTAeVOHDT/ReINDETERMINATENOTES:1. All signals switch between VOHand V

8086A.C. CHARACTERISTICSMAX MODE SYSTEM (USING 8288 BUS CONTROLLER)TIMING REQUIREMENTSSymbol Parameter8086 8086-1 8086-2UnitsTestMin Max Min Max Min M

8086Table 1. Pin DescriptionThe following pin function descriptions are for 8086 systems in either minimum or maximum mode. The ‘‘LocalBus’’ in these

8086A.C. CHARACTERISTICS (Continued)TIMING RESPONSESSymbol Parameter8086 8086-1 8086-2UnitsTestMin Max Min Max Min MaxConditionsTCLML Command Active 1

8086A.C. CHARACTERISTICS (Continued)TIMING RESPONSES (Continued)Symbol Parameter8086 8086-1 8086-2UnitsTestMin Max Min Max Min MaxConditionsTRHAV RD I

8086WAVEFORMSMAXIMUM MODE231455–1522

8086WAVEFORMS (Continued)MAXIMUM MODE (Continued)231455–16NOTES:1. All signals switch between VOHand VOLunless otherwise specified.2. RDY is sampled n

8086WAVEFORMS (Continued)ASYNCHRONOUS SIGNAL RECOGNITION231455–17NOTE:1. Setup requirements for asynchronous signals only to guarantee recognition at

8086WAVEFORMS (Continued)HOLD/HOLD ACKNOWLEDGE TIMING (MINIMUM MODE ONLY)231455–2125

8086Table 2. Instruction Set SummaryMnemonic andInstruction CodeDescriptionDATA TRANSFERMOVeMove: 76543210 76543210 76543210 76543210Register/Memory t

8086Table 2. Instruction Set Summary (Continued)Mnemonic andInstruction CodeDescriptionARITHMETIC 76543210 76543210 76543210 76543210ADDeAdd:Reg./Memo

8086Table 2. Instruction Set Summary (Continued)Mnemonic andInstruction CodeDescriptionLOGIC 76543210 76543210 76543210 76543210NOTeInvert 1111011w mo

8086Table 2. Instruction Set Summary (Continued)Mnemonic andInstruction CodeDescriptionJMPeUnconditional Jump: 76543210 76543210 76543210Direct within

8086Table 1. Pin Description (Continued)Symbol Pin No. Type Name and FunctionREADY 22 I READY: is the acknowledgement from the addressed memory or I/O

8086Table 2. Instruction Set Summary (Continued)Mnemonic andInstruction CodeDescription76543210 76543210PROCESSOR CONTROLCLCeClear Carry 11111000CMCeC

8086Table 1. Pin Description (Continued)Symbol Pin No. Type Name and FunctionS2,S1,S026– 28 O These signals float to 3-state OFF in ‘‘hold acknowledge

8086Table 1. Pin Description (Continued)Symbol Pin No. Type Name and FunctionQS1,QS024, 25 O QUEUE STATUS: The queue status is valid during the CLK cy

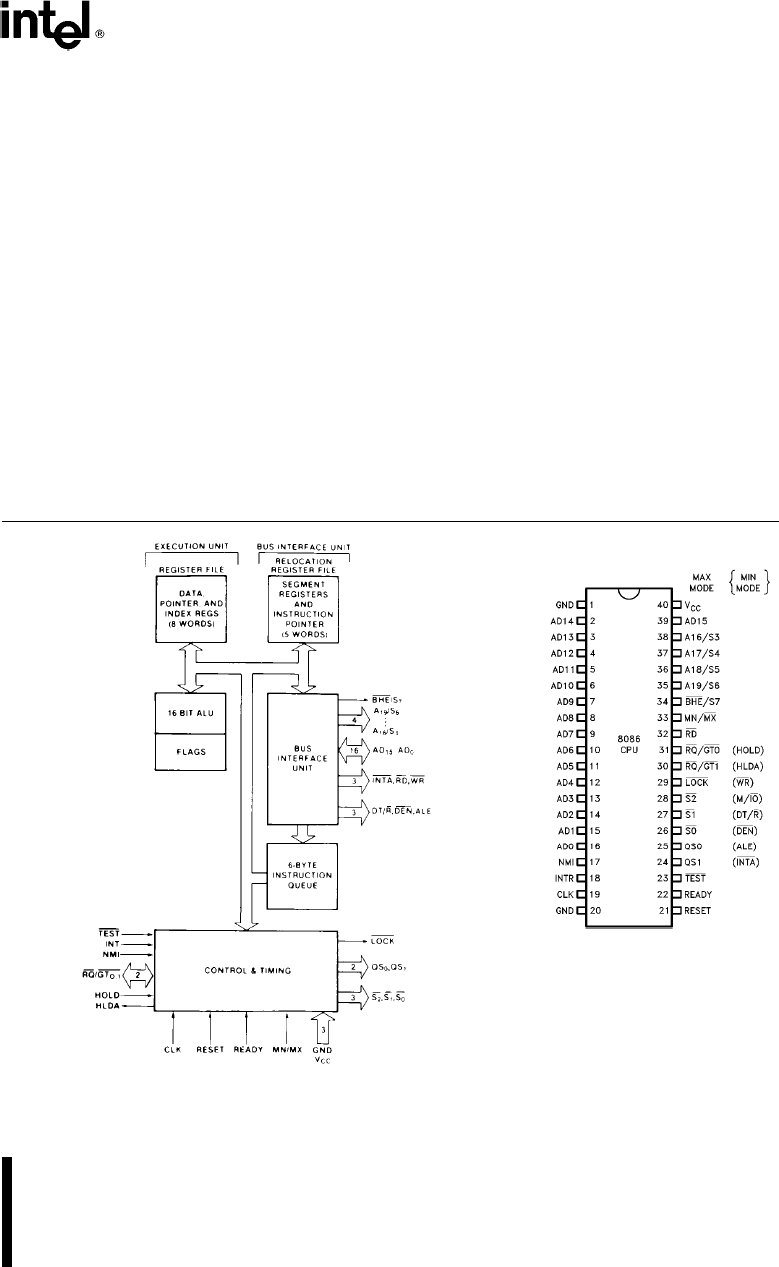

8086FUNCTIONAL DESCRIPTIONGeneral OperationThe internal functions of the 8086 processor arepartitioned logically into two processing units. Thefirst i

8086231455–3Figure 3a. Memory OrganizationIn referencing word data the BIU requires one or twomemory cycles depending on whether or not thestarting by

8086231455–5Figure 4a. Minimum Mode 8086 Typical Configuration231455–6Figure 4b. Maximum Mode 8086 Typical Configuration8

8086can occur between 8086 bus cycles. These are re-ferred to as ‘‘Idle’’ states (Ti) or inactive CLK cycles.The processor uses these cycles for inter

(78 Seiten)

(78 Seiten)

Kommentare zu diesen Handbüchern