Intel LE80537GF0414M Datenblatt Seite 36

- Seite / 97

- Inhaltsverzeichnis

- LESEZEICHEN

Bewertet. / 5. Basierend auf Kundenbewertungen

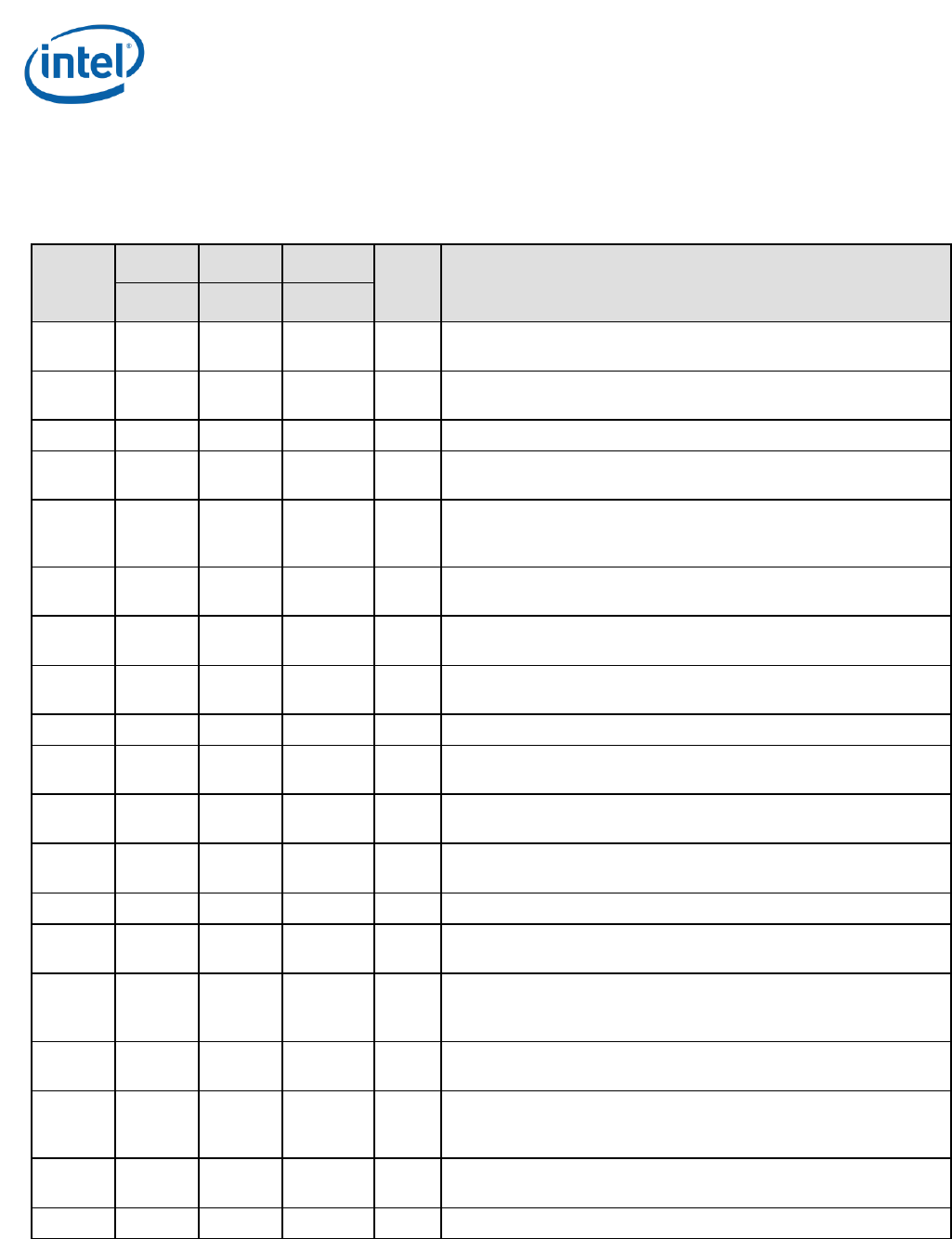

Summary Tables of Changes

36 Specification Update

Errata for Intel

®

Celeron

®

Processor 500 Series for Platforms Based

on Mobile Intel

®

965 Express Chipset Family

Number

Stepping

Stepping

Stepping

Plans

Errata

A-1

E-1

M-1

AH1

X

X

X

No Fix

Writing the Local Vector Table (LVT) When an Interrupt Is

Pending May Cause an Unexpected Interrupt

AH2

X

X

X

No Fix

LOCK# Asserted During a Special Cycle Shutdown Transaction May

Unexpectedly Deassert

AR3

No Fix

Erratum Removed

AH4

X

X

X

No Fix

VERW/VERR/LSL/LAR Instructions May Unexpectedly Update the

Last Exception Record (LER) MSR

AH5

X

X

X

No Fix

DR3 Address Match on MOVD/MOVQ/MOVNTQ Memory Store

Instruction May Incorrectly Increment Performance Monitoring

Count for Saturating SIMD Instructions Retired (Event CFH)

AH6

X

Fixed

SYSRET May Incorrectly Clear RF (Resume Flag) in the RFLAGS

Register

AH7

X

X

X

No Fix

General Protection Fault (#GP) for Instructions Greater than 15

Bytes May Be Preempted

AH8

X

X

X

No Fix

Pending x87 FPU Exceptions (#MF) Following STI May Be Serviced

Before Higher Priority Interrupts

AH9

X

X

X

No Fix

The Processor May Report a #TS Instead of a #GP Fault

AH11

X

X

X

No Fix

A Write to an APIC Register Sometimes May Appear to Have Not

Occurred

AH12

X

X

X

No Fix

Programming the Digital Thermal Sensor (DTS) Threshold May

Cause Unexpected Thermal Interrupts

AH13

X

X

X

No Fix

Count Value for Performance-Monitoring Counter

PMH_PAGE_WALK May Be Incorrect

AH14

X

X

X

No Fix

LER MSRs May Be Incorrectly Updated

AH15

X

X

X

No Fix

Performance Monitoring Events for Retired Instructions (C0H)

May Not Be Accurate

AH16

X

X

X

No Fix

Performance Monitoring Event For Number Of Reference Cycles

When The Processor Is Not Halted (3CH) Does Not Count

According To The Specification

AR16

X

Fixed

Using 2M/4M Pages When A20M# Is Asserted May Result in

Incorrect Address Translations

AH18

X

X

X

No Fix

Writing Shared Unaligned Data that Crosses a Cache Line without

Proper Semaphores or Barriers May Expose a Memory Ordering

Issue

AH19

X

X

X

No Fix

Code Segment Limit Violation May Occur On 4 Gigabyte Limit

Check

AH20

x

Fixed

FP Inexact-Result Exception Flag May Not Be Set

- Including Intel 1

- Specification Update 2

- Contents 3

- Revision History 4

- 6 Specification Update 6

- Preface 7

- Nomenclature 8

- Specification Update 9 9

- Identification Information 10

- Table 3. Intel 13

- 945 Express Chipset Family 13

- Component Markings 13

- 14 Specification Update 14

- Table 2. Intel 14

- 965 Express Chipset Family 14

- 16 Specification Update 16

- Table 1. Intel 17

- Celeron 17

- 18 Specification Update 18

- Summary Tables of Changes 19

- Specification Update 21 21

- Errata for Intel 22

- 24 Specification Update 24

- 26 Specification Update 26

- 28 Specification Update 28

- Based on Mobile Intel 29

- 30 Specification Update 30

- 32 Specification Update 32

- 34 Specification Update 34

- 38 Specification Update 38

- May Terminate Early 38

- 40 Specification Update 40

- Specification Update 43 43

- Specification Update 45 45

- Not Be Accurate 46

- Specification 47

- Address Translations 47

- Specification Update 49 49

- Specification Update 51 51

- Invocation 52

- Specification Update 53 53

- Be Incorrect 54

- Specification Update 55 55

- Specification Update 57 57

- Accurate 59

- Specification Update 61 61

- Specification Update 63 63

- Shootdown 65

- Specification Update 67 67

- Address 68

- IA32_DEBUGCTL[12] Is Set 69

- Software Interrupts 71

- Specification Update 73 73

- Specification Update 75 75

- Specification Update 77 77

- Specification Update 79 79

- Instructions as Branches 81

- Signaled 82

- Information 83

- AH108. Overlap of an Intel 84

- VM Exit 84

- Count Some Transitions 85

- Memory-Ordering Violations 86

- Specification Update 87 87

- Shutdown 88

- Specification Update 89 89

- 90 Specification Update 90

- Erratum Affecting Only Intel 91

- Core™2 Duo Mobile 91

- Processors on Mobile Intel 91

- Be Able to Enter Intel 92

- Enhanced Deeper Sleep 92

- AH6P Activation of Intel 93

- Dynamic 93

- Specification Changes 94

- Specification Update 95 95

- Specification Clarifications 96

- Documentation Changes 97

(100 Seiten)

(100 Seiten)

Kommentare zu diesen Handbüchern